IC工程师,在设计芯片时,如果是基于各种复用IP的SOC芯片,那必定要接触到AMBA总线协议。

AMBA总线是由ARM公司提出的一种开放性的片上总线标准,它独立于处理器和工艺技术,具有高速度低功耗等特点。协议的主要动机是用一种标准和高效的方法来重用这些跨多个设计的IP。

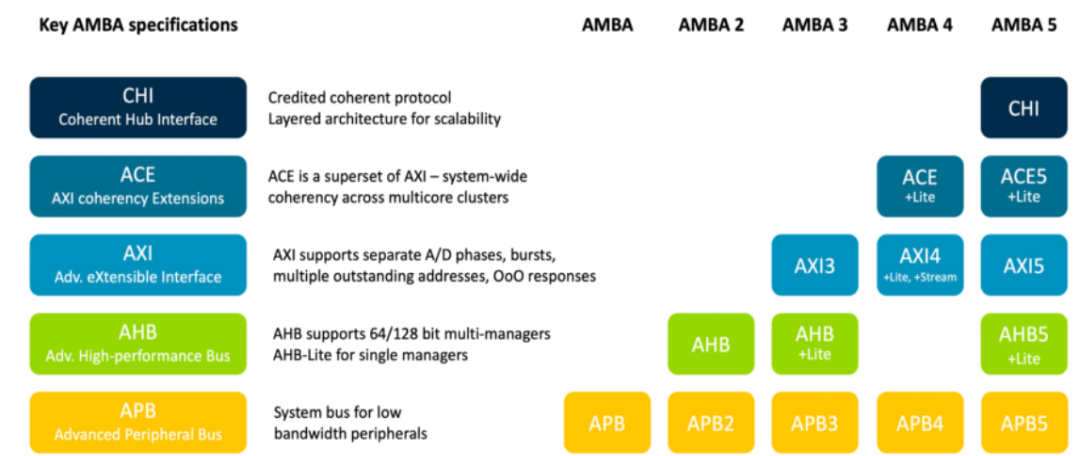

AMBA总线最常见的协议 – APB>AHB>AXI>ACE>CHI,它们的复杂度、性能和设计难度都是递增的。

CHI协议是AMBA的第五代协议,可以说是ACE协议的进化版,将所有的信息传输采用包(packet)的形式来完成。但是从接口的角度看,CHI和ACE,AXI这些协议完全不一样了。

当你在阅读这些协议的时候,你会发现:

“有些协议内容抽象难懂...”

“不明白协议为什么这么定义”

“不知道某些信号怎么用,到底在设计的时候是否要考虑这些信号”

...

你可能还会遇到更多问题...

全面解析AMBA ACE&CHI协议

移知特邀两位行业资深技术专家,精心打磨《AMBA高性能总线ACE&CHI总线协议》,本课程从协议出发,由浅入深系统且全面地系统性讲解,帮助学员解决看AMBA ACE/CHI协议时,冗长晦涩的描述与原理无法对应,导致协议看过就忘,不能形成系统性的认识,无法对体系结构中cache/存储/互联相关理论有深入的理解。

了解协议描述与真实工程中量产IP的差异,从而加深理解工程化思维,着眼于协议,超越协议看到真正的工程实现架构。

限量开课福利

前500名,免费试听

两节精品课程

扫码速抢,免费名额

▼▼▼

讲师介绍 PROFILE

Sunny

中国科学院硕士

某知名芯片公司高级验证工程师

从事数字芯片验证多年,先后就职于国内外芯片公司及创业团队,参与多个多核一致性IP及SOC一致性总线相关项目。

Jimmy

ARM/RISC-V core及AMBA 领域专家

985专业院校集成电路专业毕业

头部IC企业从事十年中大型量产项目经历,主要负责计算子系统 core + cache + interconnect + memory方向的开发。

学完你将收获

1.体系结构cache一致性MESI/MOESI的原理,软硬件实现cache coherency的方案及代价;

2.对于memory consistency/ordering相关背景原理的理解;

3.全协议ACE/ CHI.E.b transaction的解读,对应场景描述以及不同处理器的cache coherency 行为;

4.基于ACE/CHI协议的ARM CCI /CMN互联IP的实现结构,理解协议到具体实现的对应关系;

5.通过ACE与CHI的解读,理解计算机体系在cache/memory方面发展与演进方向;

6. 掌握CHI 协议的分层结构如协议层,网络层和链路层;

7. 掌握CHI 协议的流控机制、保序机制、Hazard处理和Error Handling;

8. 掌握CHI的Cache Stashing机制、Exclusive访问和DVM 操作等;

9. 掌握CHI支持的服务和性能特性等;

10. 对一致性总线和多核一致性系统有更深入的理解。

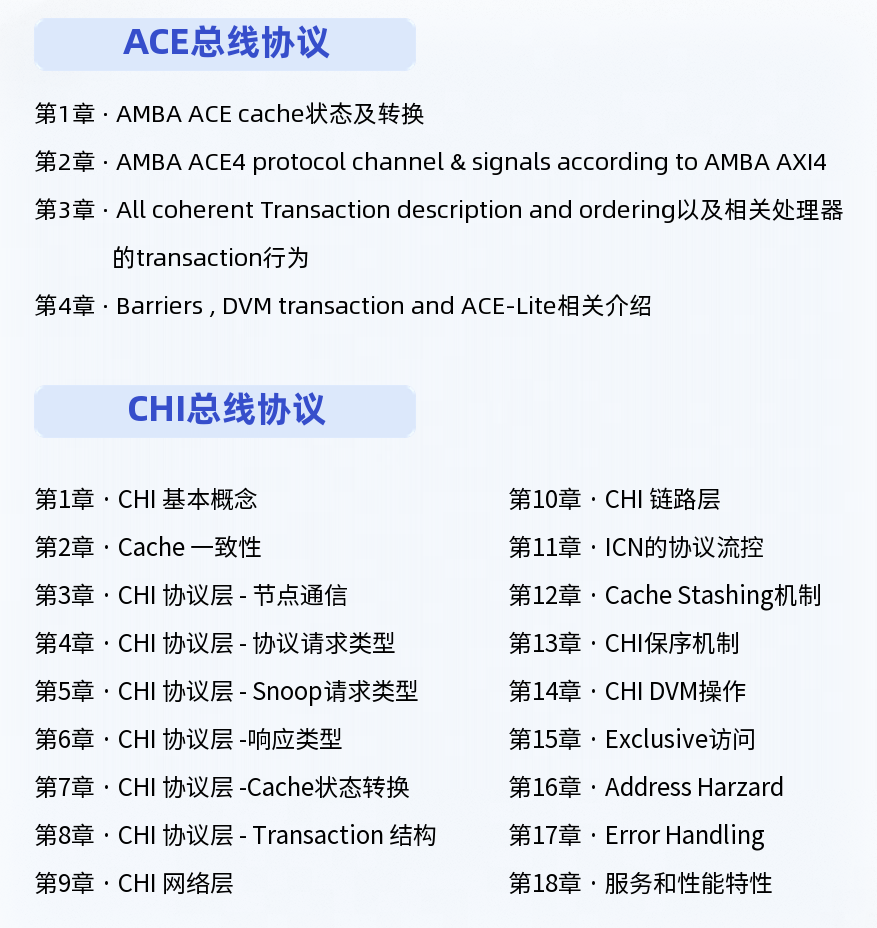

课程大纲

课程亮点

- 知识完整性:系统性讲解背景,原理,架构演进以及具体实现

- 内容适合性: 适合一致性总线相关工程师学习

- 项目竞争力:全网唯一系统性介绍CHI协议课程,增添简历亮点,提高学习效率

- 双种类教学:线上课程视频配备对应纸质教材

- 教学多样性:笔述与动画相结合,生动形象