PCIe 5.0是当前最新的PCI Express规范,提供了更高的数据传输速率和更大的带宽。

PCIe是连接两个芯片的接口,负责两个芯片通信, 连接芯片的通路为高速SerDes, 称之为链路。PCIe确保通路正常-链路训练状态机。PCIe在芯片内部是非常重要的一个大的模块,如果PCIe不能正常工作,那芯片则视为石头。

越来越多的HR开始把PCIe等高速串行接口相关经验列为了加分项,以确保可以招聘到合适而高效的验证工程师、FPGA的设计以及芯片设计工程师。学习PCIe无疑是一个值得当下就去做的一件事情。

在职场上刚接触PCIe 5.0,应用起来比较吃力,经常会遇到一些问题,今天移知小编为大家搜集了,《PCIe验证实战》第一期,学员时常问到的一些问题,以及老师的解答。希望能给大家带来帮助,建议收藏。

文末分享PCIe学习资料,私信领取。

01、PCIe 5.0学习问答

Q、RC中几个端口,是否可以进行P2P间的验证?

解答:

看RC的具体实现,比如有些RC内部只有一个port也就不能进行p2p,之前做过这样的设计采用dual ip,这样就只有一个port,目前x86 RC内部port多,支持p2p,具体看下CPU Feature.

Q、PCIe链路训练均衡的问题;

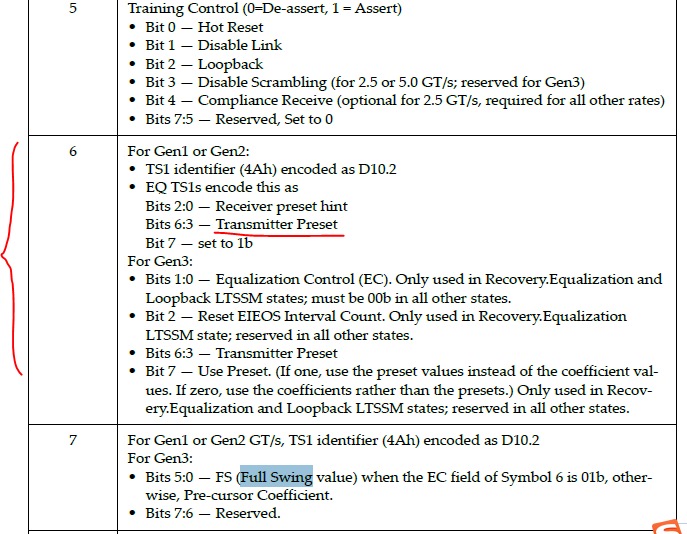

如何配置Synopsys的EP控制器的寄存器,使得在链路训练过程中修改HOST侧的PCIE PHY的TX preset值。GEN3_RELATED_OFF寄存器GEN3_EQ_CONTROL_OFF寄存器,通过配置EP的这两个寄存器配置是否可以实现,修改HOST侧的TX preset值。

解答:

1-EQ流程,RX会根据CTLE/DTE评估的情况来调节对端设备的TX FFE。

2-源码分析,不能按照问题操作

3-需要仿真-doing

Q

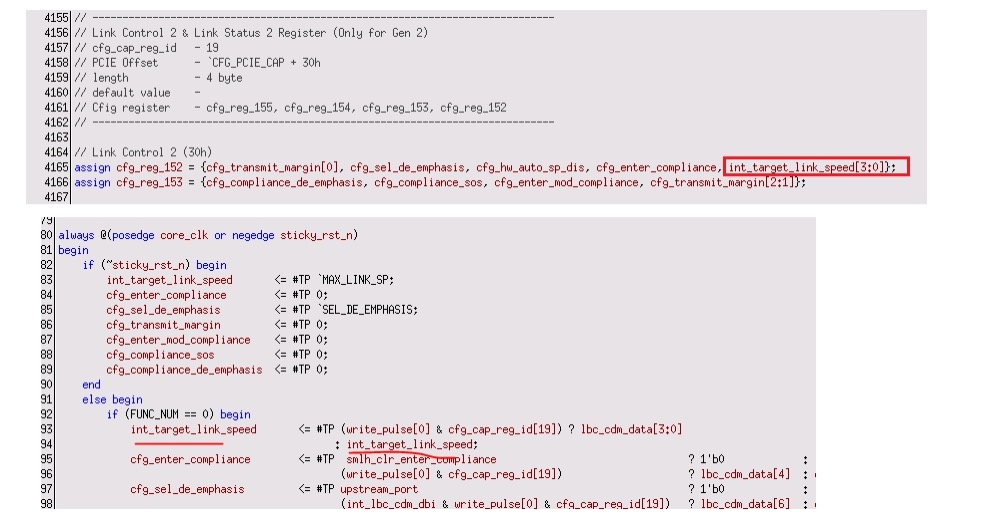

EP在detect的时候TS1发出的 datarate只支持GEN1, 最终EP 和RC也training到GEN1 ,但此时发现 RC target speed 也切到GEN1 ,这个过程是哪一部分会修改到RC的target speed吗?

解答:

1-bios到是有可能;我见过原型验证中有通过bios修改cpl timeout。

2-需要确认controller此寄存器会不会硬件自动修改,RTL代码确认不会修改。

Q、cxl下rc remote访问EP的MEMBAR0下挂的ELBI接口空间支持2DW读?

解答:

不支持,RTL代码返回CA

cxl文档里有一个ELBI2的方式,ELBI2将1K-DW(ELBI)扩展到512K-DW,这也是访问CCG Reg的方式。ELBI的空间太小,不满足要求。因此2dw的访问是ELBI2可以支持的,只是ELBI方式不支持。

Q、目标为16G,请问老师,LTSSM为什么跳过了5G,直接进入8G?

解答:

到16G的训练流程就是2.5-8-16,pcie vip还提供了一种配置直接2-16.

6.0spce看到过这方面内容的描述。

Q、PCIE序的场景,需要列举

解答:

读不超越写,请求依赖与响应因此响应不能依赖与请求,i响应包不能穿越P包(host读tag,ep写数据)。

移知《PCIe验证实战--2期》,本月强势回归,理论结合实操,全方位的学习体验,一课搞定设计和验证,本课程以可流片的PCIe代码为基础,介绍了PCIe理论以及PCIe实战的内容,目标是大家能在实际的PCIe项目中可以上手干活。共22个章节,理论和实战相结合,从验证环境的搭建,到DUT data path的梳理,学完即可上手做PCIe RTL设计以及验证工作。

即将开课,扫码咨询老师

提前抢占席位

还可领取课程费用折扣呦~

▼▼▼

02、PCIe学习资料免费领取

PCIe学习有一定的难度,想要学习好就需要不断的摸索,而PCIe的学习资料全网都是,但是真正要找干货,还要看几本经典的书。今天在这里推荐学习 PCIe 的英文资料最经典的是《PCI Express System Architecture》绝大多数的中文互联网有关 PCIe 的内容,都来自或者基于这本书。

以及《PCIe 5.0接口协议规范》,对PCIe 5.0协议的深入理解可以帮助你进行故障排除和性能优化。你能够分析和解决与协议相关的问题,如时序冲突、信号完整性、功耗管理等,从而提升系统的可靠性和性能。1000页的协议规范,读起来是很有难度的,大家保重~~

有需要的同学

可以识别二维码添加微信领取